# USB Power Delivery PHY for Domestic Applications

Liam McSherry 40313040

Submitted in partial fulfilment of the requirements for a B.Eng (Hons) in Electronic and Electrical Engineering

Supervised by Jay Hoy

School of Engineering and the Built Environment Edinburgh Napier University

March 2020

# Abstract

The USB Type-C connector is an increasingly common choice for devices of all kinds and, while it enables transmission of up to 100 watts, a consumer must still carry a mains power adapter wherever they wish to power a Type-C device. This negatively impacts convenience and, with many devices bundling an adapter, is a contributor to an increase in electronic waste. This report considers the design of a physical layer (PHY) for a USB Power Delivery plug socket which, integrated into a home, could replace many disparate mains power adapters.

In this report it is demonstrated that a semi-discrete PHY which supports both legacy and current revisions of USB Power Delivery can offer a cost-competitive alternative to monolithic PHYs supporting only current revisions, with a unit cost only 17% greater than that of a monolithic PHY. The design of the PHY is partially verified by simulation, and prototype-derived estimations indicate that the area the semi-discrete solution demands is less than half that available on the front face of a BS 4662 standard plug socket. Overall, it is concluded that a design of this kind is both economically and technologically viable.

# USB Power Delivery PHY for Domestic Applications 2019–2020 © Liam McSherry

A report, submitted in partial fulfilment of the requirements for a bachelor's degree with honours in electronic and electrical engineering, on the theory, design, and construction of a physical layer for a USB Power Delivery plug socket.

Set in IBM Plex and Rasmus Andersson's Inter.

With acknowledgement to Jay Hoy, for his guidance and supervision, and to Jim Gordon, for his prompt and highquality work in assembling prototype hardware.

# Background

The proliferation of the Universal Serial Bus (USB) has fundamentally changed how consumers interact with their computers. Although becoming more complex as it has developed, the largely singular connector for power and data and the simplification of device set-up has greatly expanded the functionality available to the consumer whilst maintaining a consistent level of convenience.

As this expansion took place, the demands of the consumer and the devices they used also expanded. However, while rates of data transfer have improved more than exponentially since USB's release in 1996, the basic level of power available to a USB device has always increased more conservatively. In fact, that basic level remained at 2.5 watts from 1996 until the 2008 publication of the USB 3.0 specification, which provided for an increase to 4.5 watts. In the time between, likely prompted by the development of the smartphone and the *de facto* standards to enable faster charging which consequently appeared, a USB Battery Charging Specification was published to provide a formalised method of accessing up to 7.5 watts of power, depending on the capabilities of the charger.

In 2012, recognising USB's shift from an interface used for data first to one used for power first, the USB Promoter Group published the USB Power Delivery Specification (USB-PD), which supports the provision of power up to 100 watts in either direction. The Promoter Group intended to obviate the need for external power supplies and enable devices which also required a data interface—such as printers, displays, and hard disk drives—to consolidate onto a single interface.

With this power-first approach, USB is increasingly becoming the all-purpose interface for portable computing. For example, a laptop might now use USB to provide a video signal to a monitor that includes a USB-PD controller and a USB hub, charging the laptop and providing access to a keyboard and mouse at the same time. Once finished, the laptop's user would need only to unplug a single cable. If this consolidation continues and USB becomes even more common, it will likely become desirable to further streamline usage and avoid power bricks in favour of a single kind of cable. In this situation, a space in the market is likely to open for a USB-PD source which replaces a conventional plug socket.

# **Abbreviated Contents**

| Abstract                                                      | 2   |

|---------------------------------------------------------------|-----|

| Background                                                    | 3   |

| Abbreviated Contents                                          | 4   |

| Contents                                                      | 5   |

| Figures                                                       | 10  |

| Tables                                                        | 12  |

| CHAPTER 1<br>Project Brief                                    | 13  |

| CHAPTER 2<br>Fundamental Theory                               | 14  |

| CHAPTER 3<br>Requirements Specification                       | 26  |

| CHAPTER 4<br>Summary of Findings                              | 33  |

| <b>CHAPTER 5</b><br>Biphase Mark Code Transceiver             | 35  |

| <b>CHAPTER 6</b><br>Binary Frequency-Shift Keying Transceiver | 47  |

| <b>CHAPTER 7</b><br>USB Type-C Signalling                     | 58  |

| CHAPTER 8<br>System Realisation                               | 60  |

| CHAPTER 9<br>Review                                           | 66  |

| APPENDIX A<br>Circuit Realisation                             | 82  |

| APPENDIX B<br>System Controller                               | 104 |

| References                                                    | 127 |

# Contents

|                              |       | Abstract                                |    |  |  |

|------------------------------|-------|-----------------------------------------|----|--|--|

|                              |       | Background                              |    |  |  |

|                              |       | Abbreviated Contents                    |    |  |  |

|                              |       | Contents                                | 5  |  |  |

|                              |       | Figures                                 | 10 |  |  |

|                              |       | Tables                                  | 12 |  |  |

| СНАРТ                        | ER 1  | Project Brief                           | 13 |  |  |

| 1.1                          |       | Context                                 | 13 |  |  |

| 1.2                          |       | Aim                                     | 13 |  |  |

| 1.3                          |       | Objectives                              |    |  |  |

| CHAPTER 2 Fundamental Theory |       | 14                                      |    |  |  |

| 2.1                          |       | Design feasibility                      |    |  |  |

| 2.2                          |       | USB Power Delivery                      | 15 |  |  |

|                              | 2.2.1 | The USB-PD protocol layer               | 16 |  |  |

|                              | 2.2.2 | The USB-PD physical layer               | 18 |  |  |

|                              | 2.2.3 | Biphase mark coding (BMC)               | 20 |  |  |

|                              | 2.2.4 | Binary frequency-shift keying (BFSK)    | 21 |  |  |

| 2.3                          |       | USB Type-C                              | 21 |  |  |

| 2.4                          |       | USB Battery Charging                    |    |  |  |

| СНАРТ                        | ER 3  | Requirements Specification              | 26 |  |  |

| 3.1                          |       | Power supply requirements               | 26 |  |  |

| 3.2                          |       | Physical layer behavioural requirements |    |  |  |

| 3.3                          |       | BMC transceiver requirements            | 28 |  |  |

| 3.4                          |       | BFSK transceiver requirements           |    |  |  |

| 3.5                          |       | Type-C signalling requirements 3        |    |  |  |

| СНАРТ            | ER 4                                        | Summary of Findings                                 |    |  |  |

|------------------|---------------------------------------------|-----------------------------------------------------|----|--|--|

| СНАРТ            | ER 5                                        | Biphase Mark Code Transceiver                       | 35 |  |  |

| 5.1 Key concerns |                                             | 35                                                  |    |  |  |

|                  | 5.1.1                                       | DC bias in received signals                         |    |  |  |

|                  | 5.1.2                                       | Synchronisation                                     | 35 |  |  |

| 5.2              |                                             | Transmitter design                                  | 36 |  |  |

|                  | 5.2.1                                       | Transmitter control logic                           | 36 |  |  |

|                  | 5.2.2                                       | Transmitter line driver                             | 37 |  |  |

| 5.3              |                                             | Receiver design                                     | 39 |  |  |

|                  | 5.3.1                                       | Synchronisation logic                               | 39 |  |  |

|                  | 5.3.2                                       | Decoding logic                                      | 41 |  |  |

|                  | 5.3.3                                       | Line instrumentation                                | 42 |  |  |

| СНАРТ            | ER 6                                        | Binary Frequency-Shift Keying Transceiver           | 47 |  |  |

| 6.1              |                                             | Key concerns                                        | 47 |  |  |

|                  | 6.1.1                                       | Speed of operation                                  |    |  |  |

|                  | 6.1.2                                       | Synchronisation                                     |    |  |  |

| 6.2              |                                             | Transmitter design                                  | 47 |  |  |

|                  | 6.2.1                                       | Modulator design                                    | 47 |  |  |

|                  | 6.2.2 Control logic: four-oscillator design |                                                     | 51 |  |  |

|                  | 6.2.3                                       | Control logic: Colpitts design                      | 52 |  |  |

| 6.3              |                                             | Receiver design                                     | 53 |  |  |

|                  | 6.3.1                                       | Demodulator design                                  | 53 |  |  |

|                  | 6.3.2                                       | Automatic gain controller                           | 55 |  |  |

|                  | 6.3.3                                       | Timing and decoding logic: time-averaging design    | 55 |  |  |

|                  | 6.3.4                                       | Timing and decoding logic: frequency–voltage design |    |  |  |

|                  | 6.3.5 Squelch detection                     |                                                     |    |  |  |

| СНАРТ            | ER 7                                        | USB Type-C Signalling                               | 58 |  |  |

| 7.1              |                                             | Rp–Rd signalling                                    | 58 |  |  |

| 7.2              |                                             | Cable power                                         | 58 |  |  |

| CHAPTER 8 System Realisation |       | 60                                                 |    |  |  |

|------------------------------|-------|----------------------------------------------------|----|--|--|

| 8.1                          |       | Design for excellence                              | 60 |  |  |

|                              | 8.1.1 | Design for manufacturing                           |    |  |  |

|                              | 8.1.2 | Design for test                                    | 61 |  |  |

|                              | 8.1.3 | Design for safety                                  | 62 |  |  |

| 8.2                          |       | Test-driven development                            | 62 |  |  |

|                              | 8.2.1 | Integration testing                                | 64 |  |  |

|                              | 8.2.2 | Unit testing                                       | 64 |  |  |

|                              | 8.2.3 | Formal verification                                | 64 |  |  |

| СНАРТ                        | ER 9  | Review                                             | 66 |  |  |

| 9.1                          |       | Project schedule                                   | 66 |  |  |

| 9.2                          |       | Designs                                            | 67 |  |  |

|                              | 9.2.1 | BMC transceiver circuit                            | 67 |  |  |

|                              | 9.2.2 | BFSK transceiver circuit                           | 68 |  |  |

|                              | 9.2.3 | System controller: BMC transmitter                 | 68 |  |  |

|                              | 9.2.4 | System controller: BMC receiver                    |    |  |  |

|                              | 9.2.5 | System controller: FPGA resource utilisation       | 70 |  |  |

| 9.3                          |       | Objectives                                         | 72 |  |  |

|                              | 9.3.1 | Implementing the USB Power Delivery physical layer | 72 |  |  |

|                              | 9.3.2 | Supporting legacy communication modes              | 73 |  |  |

|                              | 9.3.3 | Offering a cost-competitive solution               | 74 |  |  |

|                              | 9.3.4 | Supporting installation in place of a plug socket  | 75 |  |  |

|                              | 9.3.5 | Complying with standards and law                   | 77 |  |  |

| 9.4                          |       | Professional competence                            | 78 |  |  |

| 9.5                          |       | Conclusion                                         | 80 |  |  |

|       |         | APPENDIX A                          |     |

|-------|---------|-------------------------------------|-----|

|       |         | Circuit Realisation                 | 82  |

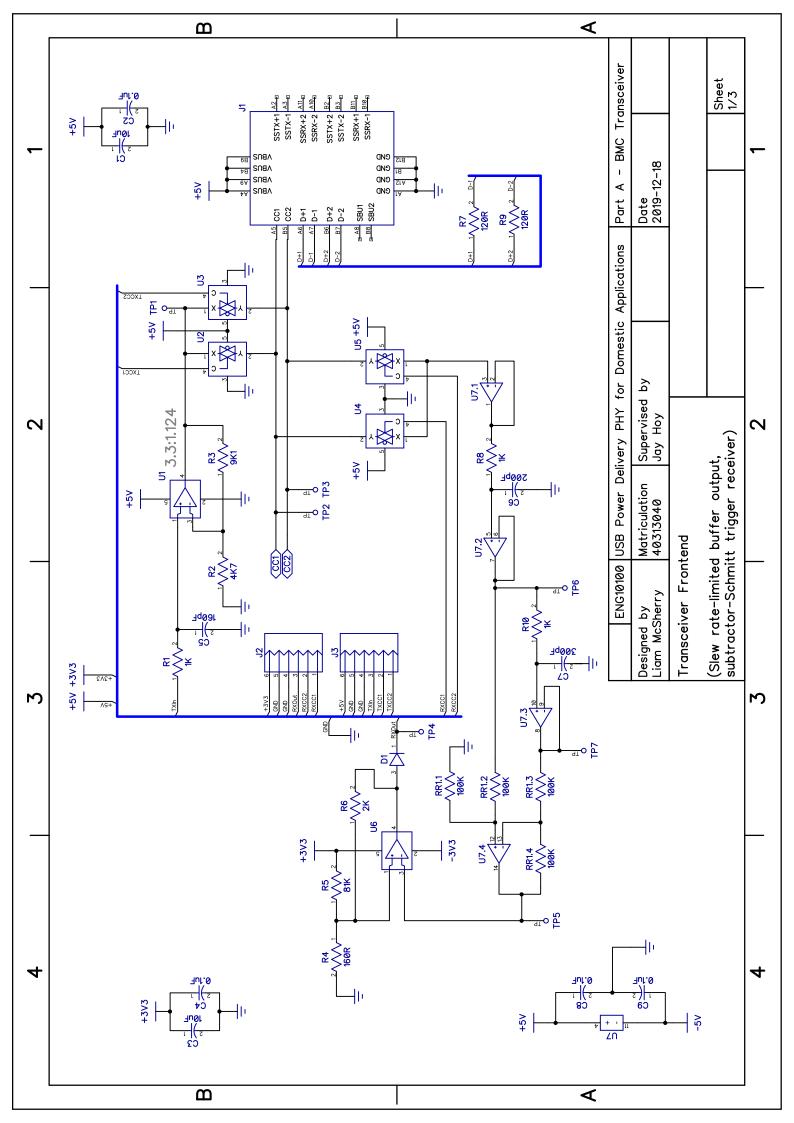

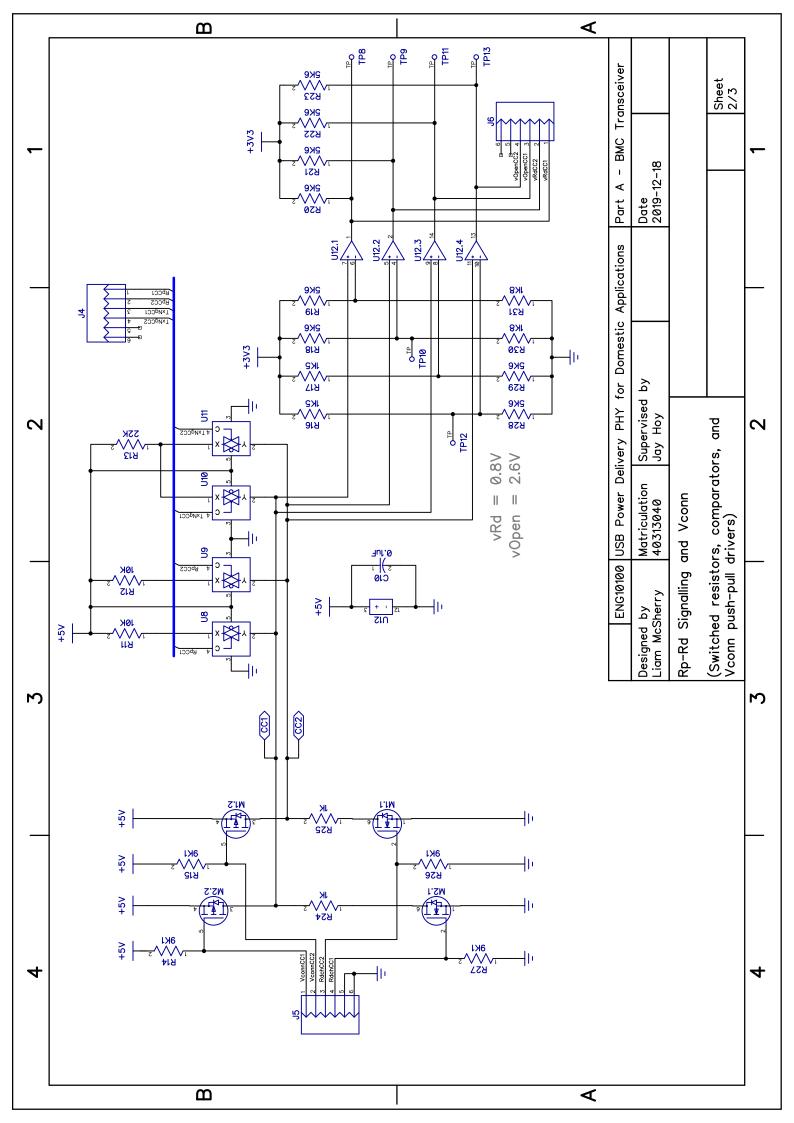

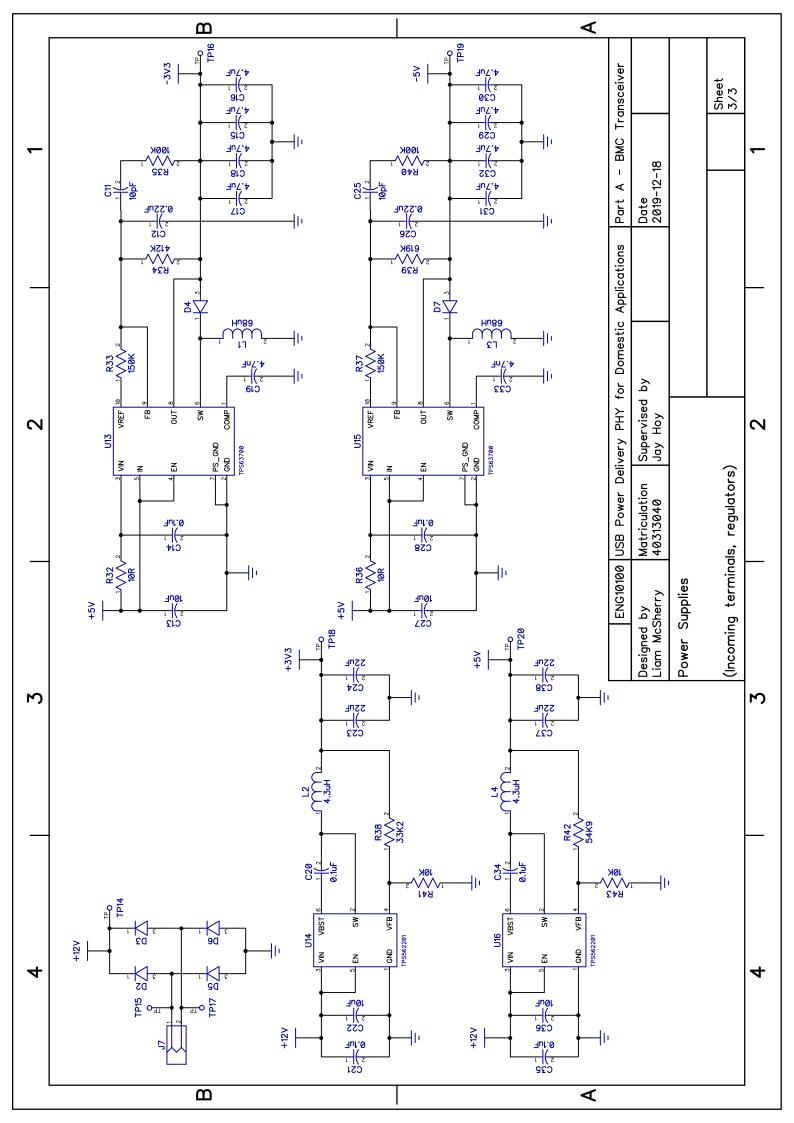

| СНАРТ | ER A1   | Schematic Diagrams                  | 83  |

| СНАРТ | ER A2   | Circuit Layout                      | 89  |

| СНАРТ | ER A3   | Bill of Materials                   | 90  |

| A3.1  |         | System controller                   | 93  |

| A3.2  |         | BMC transmitter                     | 94  |

|       | A3.2.1  | Slew rate-limited buffer            | 94  |

|       | A3.2.2  | Transmission gate                   | 95  |

| A3.3  | 1       | BMC receiver                        | 95  |

|       | A3.3.1  | Subtractor                          | 95  |

|       | A3.3.2  | Schmitt trigger                     | 96  |

| A3.4  |         | BFSK four-oscillator transmitter    | 96  |

| A3.5  | i       | BFSK Colpitts transmitter           | 97  |

|       | A3.5.1  | Colpitts oscillator                 | 97  |

|       | A3.5.2  | Varactor control                    | 98  |

| A3.6  | )       | BFSK automatic gain controller      | 99  |

| A3.7  | ,       | BFSK squelch detector               | 100 |

| A3.8  | 5       | BFSK time-averaging receiver        | 100 |

| A3.9  | )       | BFSK frequency–voltage receiver     | 101 |

| A3.1  | .0      | BFSK bandpass filter                | 101 |

| A3.1  | .1      | Type-C signalling                   | 101 |

|       | A3.11.1 | 1 Rp switches                       | 101 |

|       | A3.11.2 | 2 Attachment detectors              | 101 |

|       | A3.11.3 | 3 Cable power and discharge drivers | 102 |

| A3.1  | .2      | Power supply                        | 102 |

|       | A3.12.2 | 1 Protection                        | 102 |

|       | A3.12.2 | 2 Positive-supply regulators        | 102 |

|       | A3.12.3 | 3 Negative-supply regulators        | 103 |

|            | APPENDIX B                     |     |  |  |

|------------|--------------------------------|-----|--|--|

|            | System Controller              | 104 |  |  |

| CHAPTER B1 | Overview                       | 105 |  |  |

| CHAPTER B2 | Biphase Mark Code Transmitter  | 106 |  |  |

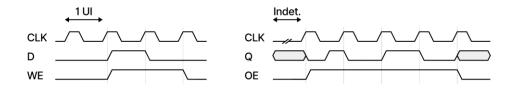

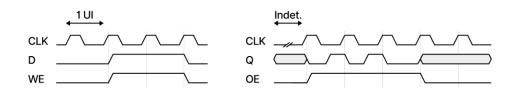

| B2.1       | Transmitter line-driving block | 106 |  |  |

| B2.2       | Preamble generator             | 108 |  |  |

| B2.3       | 4b5b encoder                   | 110 |  |  |

| B2.4       | 4b5b decoder                   | 112 |  |  |

| B2.5       | Control unit 11                |     |  |  |

| B2.6       | 5-bit Gray code generator      | 116 |  |  |

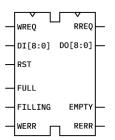

| B2.7       | FIFO9 block                    | 117 |  |  |

| CHAPTER B3 | Biphase Mark Code Receiver     | 119 |  |  |

| B3.1       | Binary search block            | 119 |  |  |

| B3.2       | Cyclic redundancy check engine | 121 |  |  |

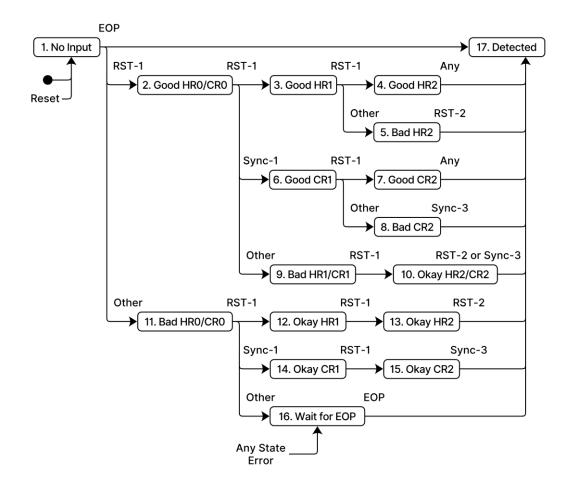

| B3.3       | End-of-packet detector         | 122 |  |  |

| B3.4       | Control unit                   | 124 |  |  |

|            |                                |     |  |  |

References

127

# Figures

| No.       | Caption P                                                                                             | age |  |  |

|-----------|-------------------------------------------------------------------------------------------------------|-----|--|--|

| Figure 1  | An example USB-PD negotiation.                                                                        | 17  |  |  |

| Figure 2  | The general format of USB-PD packets.                                                                 | 19  |  |  |

| Figure 3  | Biphase mark coding (BMC) of example binary data.                                                     | 21  |  |  |

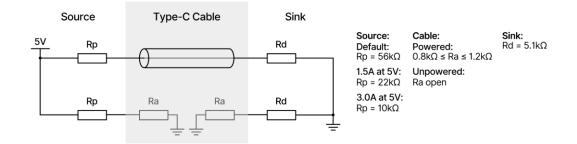

| Figure 4  | Presence and role resistances (Rp–Rd) on the USB Type-C<br>'CC' wire.                                 | 22  |  |  |

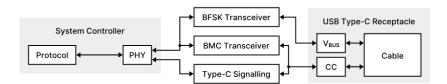

| Figure 5  | Block diagram of the project system.                                                                  | 26  |  |  |

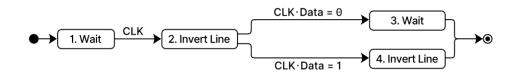

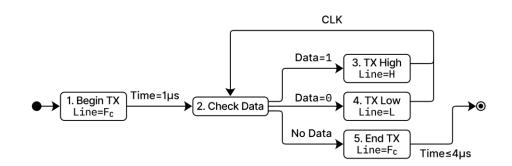

| Figure 6  | State diagram of basic BMC transmitter operation.                                                     | 36  |  |  |

| Figure 7  | State diagram of a USB-PD BMC transmitter's operation.                                                | 36  |  |  |

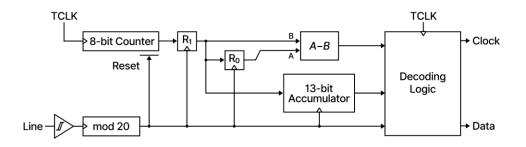

| Figure 8  | High-level design of the BMC receiver synchronisation logic.                                          | 41  |  |  |

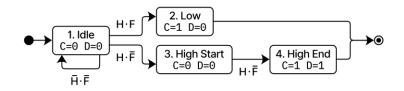

| Figure 9  | State diagram of the BMC receiver decoding logic's operation.                                         | 42  |  |  |

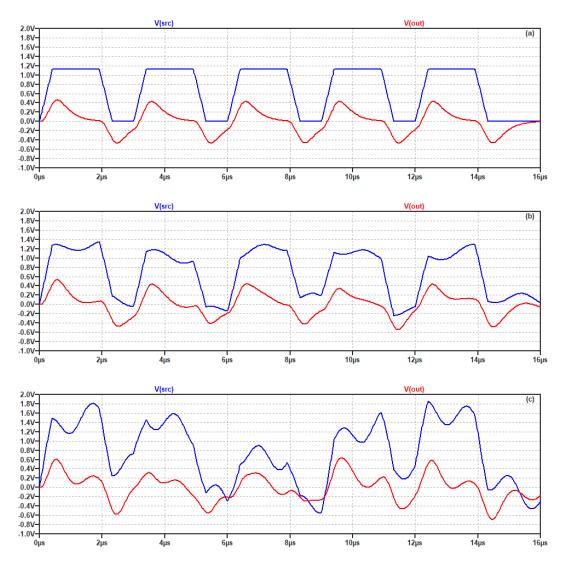

| Figure 10 | The output of the USB-PD receiver subtraction scheme for various levels of noise-affected input.      |     |  |  |

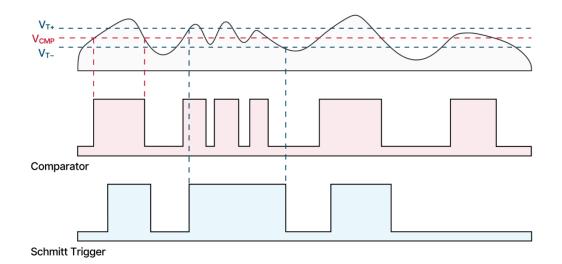

| Figure 11 | Operation of a comparator and a Schmitt trigger on a noisy signal.                                    | 44  |  |  |

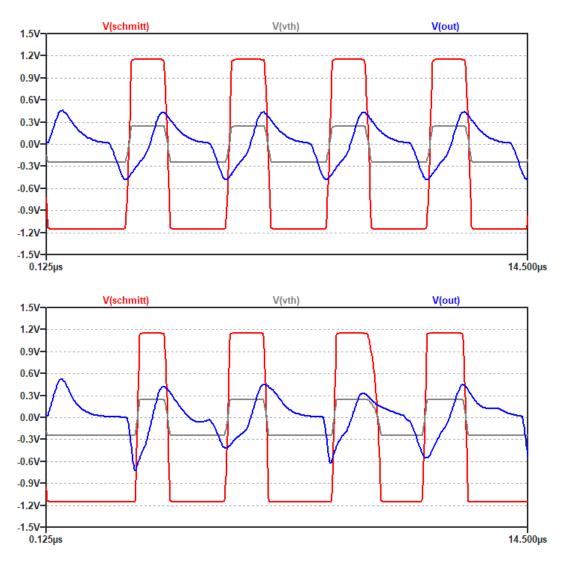

| Figure 12 | Schmitt trigger operation on BMC receiver subtractor output.                                          | 45  |  |  |

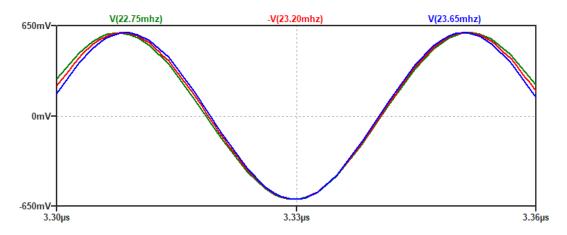

| Figure 13 | The phase difference of 23.2MHz±450kHz waves returning to zero at the end of a data period of 3.33µs. | 48  |  |  |

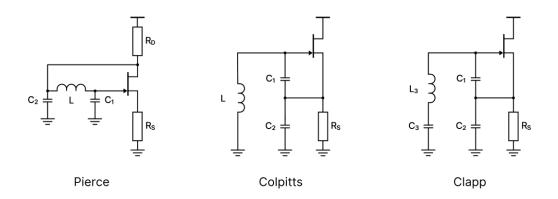

| Figure 14 | Comparison of topologies of LC sine wave oscillators.                                                 | 50  |  |  |

| Figure 15 | High-level design of the four-oscillator BFSK transmitter.                                            | 51  |  |  |

| Figure 16 | State diagram for the four-oscillator BFSK transmitter<br>line logic.                                 | 52  |  |  |

| Figure 17 | FSK demodulation with cascaded multivibrators.                                                        | 54  |  |  |

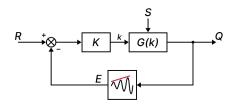

| Figure 18 | Block diagram of the automatic gain controller.                                                       | 55  |  |  |

| Figure 19 | High-level design of the time-averaging BFSK receiver.                                                | 56  |  |  |

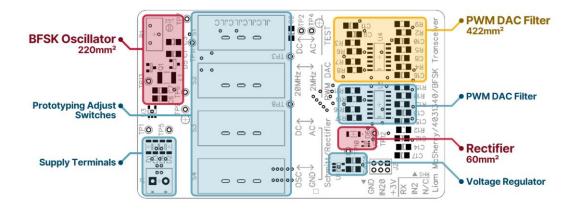

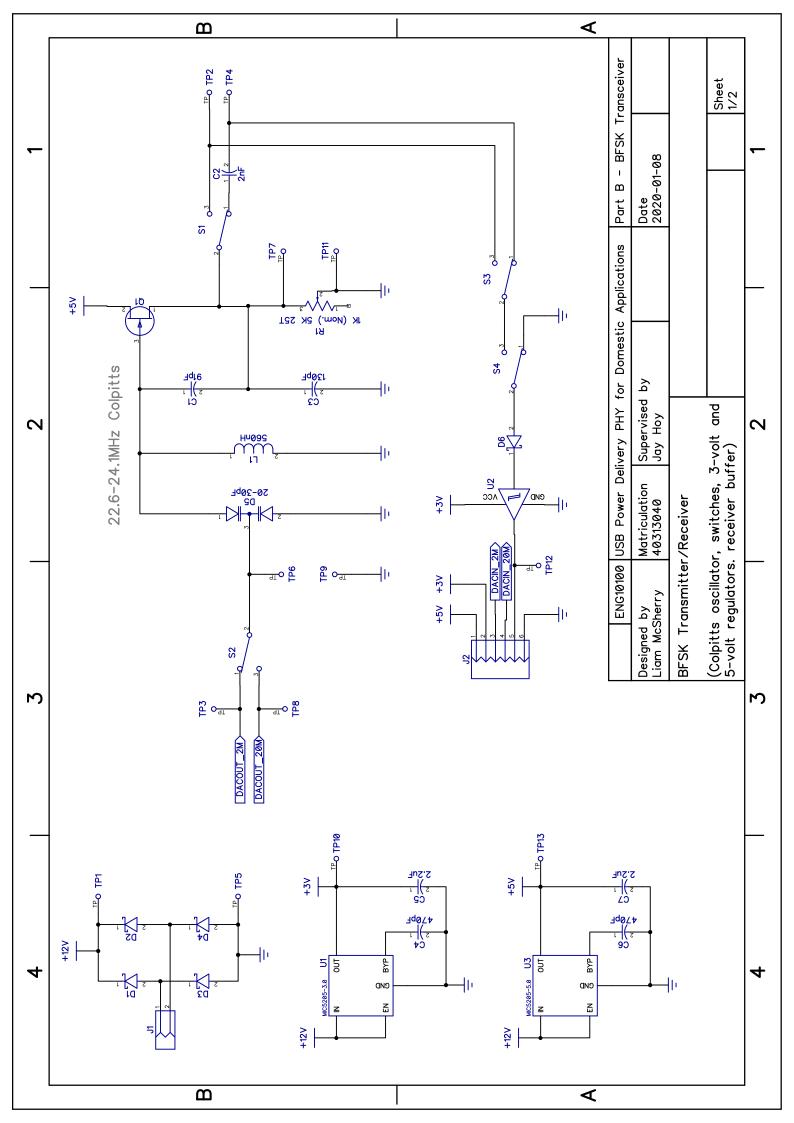

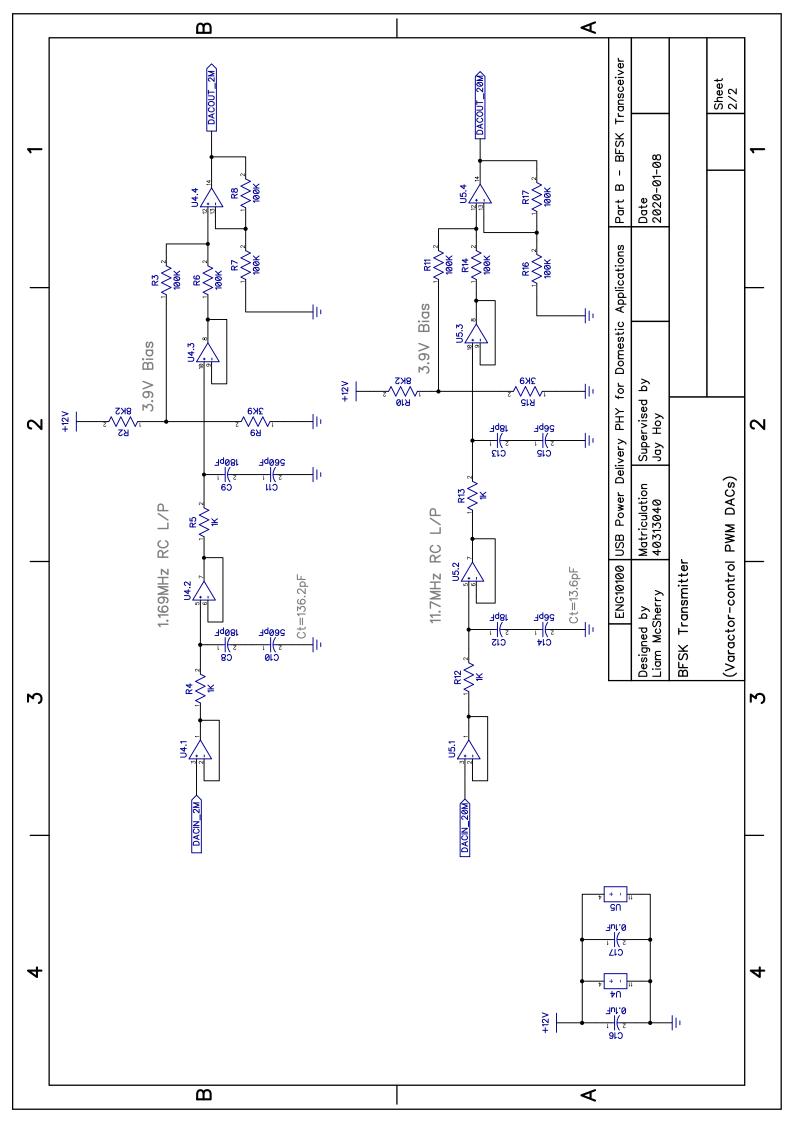

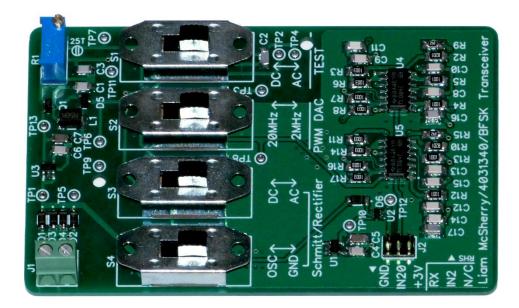

| Figure 20 | Annotated diagram of the BFSK printed circuit board.                                                  | 76  |  |  |

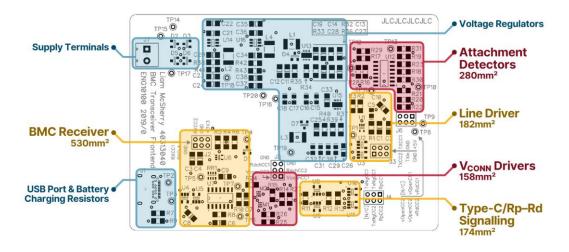

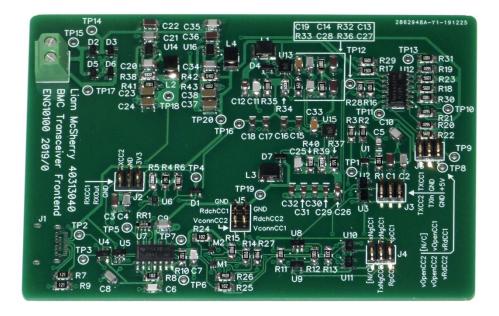

| Figure 21 | Annotated diagram of the BMC printed circuit board.                                                   | 76  |  |  |

| No.       | Caption                                                | Page |

|-----------|--------------------------------------------------------|------|

| Figure A1 | BMC transceiver circuit layout.                        | 89   |

| Figure A2 | BFSK transceiver circuit layout.                       | 89   |

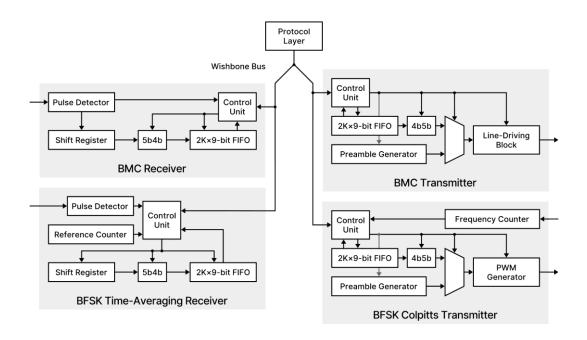

| Figure B1 | A high-level block diagram of the system controller.   | 105  |

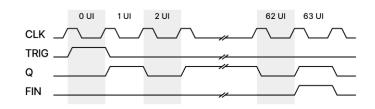

| Figure B2 | Biphase mark-coded transmission of sequence 10.        | 107  |

| Figure B3 | Biphase mark-coded transmission of sequence 11.        | 107  |

| Figure B4 | The output waveform for the USB-PD preamble generator. | 108  |

| Figure B5 | State diagram for the end-of-packet detector.          | 123  |

# Tables

| No.      | Caption                                                            | Page |

|----------|--------------------------------------------------------------------|------|

| Table 1  | USB-PD physical layer ordered sets.                                | 19   |

| Table 2  | PLL divisors and multipliers for a four-oscillator BFSK modulator. | 49   |

| Table 3  | System controller FPGA resource utilisation.                       | 71   |

| Table 4  | Cost comparison of semi-discrete and monolithic solutions.         | 74   |

| Table 5  | Review of project against CEng standard.                           | 79   |

| Table A1 | Bill of materials for the BMC transceiver circuit.                 | 90   |

| Table A2 | Bill of materials for the BFSK transceiver circuit.                | 92   |

| Table B1 | Map of 4b5b encoder input to K-codes.                              | 111  |

| Table B2 | Register map for the BMC transmitter control unit.                 | 114  |

| Table B3 | Error codes for the BMC transmitter control unit.                  | 115  |

| Table B4 | Register map for the BMC receiver control unit.                    | 125  |

| Table B5 | Error codes for the BMC receiver control unit.                     | 126  |

# 1. Project Brief

## 1.1 Context

A power supply which conforms to the Universal Serial Bus Power Delivery Specification (USB-PD) and which can be installed in the place of a conventional plug socket is required to meet anticipated market demand. Current offerings for monolithic USB-PD controllers are limited in their flexibility and support for legacy interfaces, and so it is to be investigated whether a non-monolithic design can offer a viable and cost-competitive alternative.

## 1.2 Aim

The aim of the project is to design and build with semi-discrete components a USB Power Delivery physical layer suitable for integration into a power supply in a conventional plug socket form factor.

## 1.3 Objectives

1.3.1 Implementing the USB Power Delivery physical layer

The project should produce a design which, as far as necessary in the context, implements the USB-PD physical layer (PHY) and hence enables communication using the biphase mark coding scheme (BMC) required to implement USB-PD.

## 1.3.2 Supporting legacy communication modes

The project should investigate the viability of including in the produced design support for communication using the legacy binary frequency-shift keying scheme (BFSK) specified in USB-PD revision 2.0.

## 1.3.3 Offering a cost-competitive solution

The design produced by the project should offer a unit cost at reasonable volume which compares favourably to a monolithic USB-PD controller solution.

## 1.3.4 Supporting installation in place of a plug socket

The design produced by the project should be suitable, with minimal further work, for integration with other components in a housing that allows installation in a space intended for a conventional plug socket.

## 1.3.5 Complying with standards and law

The project should identify relevant requirements in standards and law and should produce a design which, as far as necessary in the context, complies with the identified requirements.

# 2. Fundamental Theory

The objectives in chapter 1 set the scope of the project but are not sufficient *per se* to guide a design; they are abstract and describe the requirements of the user rather than the requirements of the designer. This chapter discusses the theory and background that are the foundation for the concrete design and functional requirements defined in chapter 3.

## 2.1 Design feasibility

The concept of a USB Power Delivery-based plug socket is not a new one—proof of the concept was presented by Reydams and Lauwereys *et al.* [1] in 2014 and, in their 2018 analysis, Vossos *et al.* [2] considered USB-PD as a candidate standard for use in DC power distribution throughout commercial premises.

The work by Reydams and Lauwereys *et al.* indicates that space constraints are unlikely to be prohibitive even when designing to supply the 100-watt maximum the USB Power Delivery Specification standardises, with their unhoused design measuring in the region of  $45 \times 45 \times 90$ mm (W×D×H). Although their design exceeds BS 4662 [3] plug socket size limits<sup>1</sup> and a housing will add to product size, the transition from a prototype to a commercial design is likely to enable miniaturisation. For example, the circuit board shown in their figure 5 has large areas which are visibly bare. That said, the work Reydams and Lauwereys *et al.* present focuses on the power electronics aspects of the design—at the time of their writing, they note, USB Power Delivery was relatively fresh to the market and so no commercial devices were available for purchase. Consequently, as their design emulated rather than implemented USB-PD, the practicalities of its implementation are not discussed.

Narrowing from the general feasibility of a USB-PD plug socket, it is obvious that implementing the Power Delivery physical layer is feasible. The uncertainty lies in the feasibility of a cost-competitive semi-discrete implementation.

At the lowest end of the cost range, monolithic 'port controllers' provide a PHY and a partial implementation of the protocol layer. A separate system controller is required to carry out most USB-PD tasks but, that aside, a first impression might suggest that components such as the FUSB302 [4] (£0.359 at 3ku), the PTN5110 [5] (£0.564 at 4ku), or the UPD350A [6] (£0.72 at 5ku) are the ideal tools for the application. However, their use is limited—these devices support only the biphase mark code scheme, and so additional hardware would be required to

<sup>&</sup>lt;sup>1</sup> A flush-to-wall one-gang box has a square cavity 68.3mm wide and up to 47mm deep if compliant with BS 4662, fig. 1.

support the binary frequency-shift keying scheme. As the PHY included in these port controllers is integral and not exposed, any additional hardware would have to duplicate the PHY implementation as well as providing co-ordination between the two independent PHYs. A semi-discrete solution with a single PHY attached to two transceivers would reduce redundancy and allow the cost of additional hardware to be distributed between BMC and BFSK transceivers. This has the potential to enable cost competitiveness.

Moving from somewhat barebones USB Type-C port controllers, full-featured charging controllers are available at increased cost. These devices integrate the controller needed to perform protocol-layer tasks and often support standards which supplement USB-PD. The AP43770 [7] (£1.08 at 4ku), for example, offers support for USB Battery Charging, Qualcomm QuickCharge,<sup>2</sup> and USB-PD's programmable power supply features. Devices of this kind share limitations with the more basic port controllers, but more pressing is their flexibility—these parts are fixed to a relatively narrow range of functionality, and any deviation outside this range would require a further controller. This might necessitate a high-cost processing element if more than basic power converter interfacing is required or if the networking that Reydams and Lauwereys *et al.* envisage is implemented.

Added to this, as a turnkey solution, any derived product is entirely dependent on the utilities a manufacturer provides to program the device. For a product which, compared to a microcontroller, is relatively obscure, the support life of these tools is a concern that cannot be ignored. Notably, the AP43770 datasheet provides no information on programming. Brief examination of the devices available shows that support and quality of documentation follow price. The TPS65988 [8] (£2.81 at 2.5ku) offers far better documentation and integrates  $V_{CONN}$  and  $V_{BUS}$  power switches, but sacrifices QuickCharge support and uses an external memory. The extent of the integration it offers is likely to make it the benchmark in assessing whether a semi-discrete design is cost-competitive.

Overall, these observations suggest that—while it is far from clear-cut—there is the potential for a semi-discrete solution to offer improved compatibility and value as compared to a monolithic solution.

#### 2.2 USB Power Delivery

Although it comes under the broad 'USB' label, USB Power Delivery as a standard is largely independent of the other components of USB. Negotiation between Power Delivery devices happens over a channel entirely separate from that used by USB devices to communicate with their hosts and, except under special

<sup>&</sup>lt;sup>2</sup> Qualcomm markets QuickCharge as its own high-power USB-based charging specification. The text of the specification is not publicly available, but press coverage indicates that version 4 is compatible with USB-PD.

circumstances,<sup>3</sup> USB data flow and the USB-PD negotiation flow do not influence each other. Indeed, USB data support is intentionally an optional part of USB-PD.<sup>4</sup>

Like USB, the USB-PD specification defines both a physical layer—dealing with the generation, transmission, and interpretation of electrical signals—and a protocol layer, which describes how transmitted data is used to form meaningful messages and how connected devices interact. It has three major revisions, with two continuing to be published by the USB Implementers Forum.

This project will primarily work to USB-PD revision 3.0 as adopted in the 2018 edition of BS EN IEC 62680-1-2 [9]. However, where necessary for objective 1.3.2, reference will be made to revision 2.0 [10].

#### 2.2.1 The USB-PD protocol layer

At the highest level, the Power Delivery protocol layer relies on establishing a contract between the source (power supply) and sink (power consumer)—a fixed agreement on how power is to be delivered and used. The connected devices operate within the bounds of the contract until a reset condition occurs or until they agree to renegotiate and adopt a different power level.

To establish a contract, connected devices progress through four stages:

- Detection, where the source and sink detect that a cable has been attached between them and prepare to begin communication;

- Cable identification, where the source determines which kind of cable is connected to it either by reference to the standard minimum capabilities<sup>5</sup> or by interrogating electronics integrated into the cable;

- Offer, where the source lists to the sink the voltage levels it supports and the currents it can supply at each level, excluding the capabilities which exceed the ratings of the cable;<sup>6</sup>

- Agreement, where the sink requests one of the listed capabilities and the source confirms agreement, immediately followed by the source adjusting its supplied power to the requested level.

- <sup>4</sup> See, in particular, USB-PD revision 3.0 [9] at § 6.4.1.2.2.4.

- <sup>5</sup> All Type-C cables can carry 3 amps. If a USB-PD source includes Type-A or Type-B receptacles, it uses a special 'PD Detect' contact to identify high-current cables: regular cables carry 1.5 amps, micro-USB-PD cables carry 3 amps, and full-size USB-PD cables carry 5 amps. See USB-PD revision 2.0 [10] at § 3.1.1, 3.1.6, 3.2.2, and 3.4.

- <sup>6</sup> See USB-PD revision 3.0 [9] at § 4.4.

<sup>&</sup>lt;sup>3</sup> The USB-PD specification [9] defines (at § 6.3.9) a 'swap data roles' message, used to agree a role reversal where the downstream-facing port (the host) becomes the upstream-facing port (the device) and *vice versa* while maintaining the direction of power flow.

This is done using messages transmitted over the physical layer (see 2.2.2), and most communication is done using 'control' and 'data' messages (which are used to manage the connection and provide device information, respectively). USB-PD does define a third type—the extended message—with an increased payload size, but this type is not relevant to the most common USB-PD tasks.

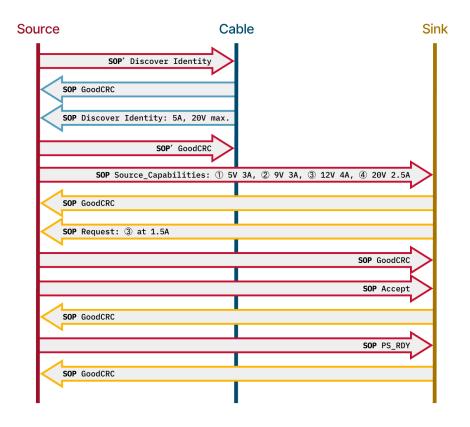

A message can be addressed to one of three recipients: the opposite Type-C port, the 'electronic marker' chip in the cable-end nearest the source, or the marker chip in the cable-end nearest the sink (if present). The specification uses the somewhat opaque terms SOP, SOP', and SOP", respectively, for these addresses. It is this addressing that enables a USB-PD source to interrogate a cable for the current it supports. A typical negotiation involves a simple and relatively short exchange of messages. An example is illustrated in figure 1.

Figure 1. An example USB-PD negotiation.

For each message in this exchange, the protocol layer defines failure conditions which, if met, can substantially alter the message flow. The most general failure conditions include the failure to receive acknowledgement<sup>7</sup> or an anticipated response, although more complex messages have other conditions related to

<sup>7</sup> An acknowledgement *GoodCRC* message must be fully received within 1ms: [9] at § 6.6.1.

their meaning—the *Request* message, for example, might fail if the sink sends an invalid request or if the source is unable to meet the request.<sup>8</sup> The response a failure elicits also differs depending on the message—in the general case, a 'soft reset' first clears protocol-layer state but leaves contracts in place and is followed by a 'hard reset' and ultimately USB Type-C error recovery if any failure cannot be resolved.<sup>9</sup> Hard resets invalidate contracts, while Type-C error recovery electrically disconnects a sink in a non-graceful manner.

More complex failures, and message sequences more generally, are driven by the policy engine—a standardised state machine dictating how interactions between the source, sink, and cable proceed.<sup>10</sup> A core concept used by the policy engine is the 'atomic message sequence' (AMS),<sup>11</sup> which is a sequence of messages which represents a single operation and which is logically indivisible. The use of a message sequence which is not a defined AMS is inherently invalid as the policy engine has no behaviour specified for that sequence. Within the set of defined AMS, each is either interruptible or non-interruptible—that is, a protocol error that occurs during the AMS either causes a general-case failure as above or causes a return to the appropriate ready state.<sup>12</sup>

A policy engine exists for each USB port, and each policy engine in a device is coordinated by a 'device policy manager' with knowledge of the entire system. The device policy manager can also implement wider 'system' policies it receives from a USB host over the USB data bus. This has limited relevance to the project.

#### 2.2.2 The USB-PD physical layer

At a lower level in the stack, the physical layer provides three relatively simple services to the protocol layer: packet framing and de-framing, message integrity verification, and media conversion.

The essential unit of transmission is the packet and, although other signalling between USB-PD devices takes place,<sup>13</sup> packets are the only means by which protocol layers can request and send information. Packets are also used to a more limited extent for basic control transmissions, and this difference in use is

- <sup>8</sup> See USB-PD revision 3.0 [9] at § 6.3.4.

- <sup>9</sup> See USB-PD revision 3.0 [9] at § 4.5.2.2.2 and 6.8.

- <sup>10</sup> See USB-PD revision 3.0 [9] at § 8.3 generally and 8.3.3.2 for USB-PD source state diagrams.

- Per USB-PD revision 3.0 [9] at § 8.3.2, an AMS is any sequence of messages which starts, ends, or both starts and ends in the 'source ready', 'sink ready', or 'cable ready' states (as appropriate for the device on which the policy engine is operating).

- <sup>12</sup> See 'interruptible' and 'non-interruptible' in USB-PD revision 3.0 [9] at § 1.6.

- For example, resistances are used to signal whether a sink is or is not permitted to transmit on the USB-PD data channel. These resistances are controlled by the source and are intended as a means of collision avoidance: USB-PD revision 3.0 [9] at § 5.7. Note that, for revision 2.0 [10], collision avoidance relies instead on voltage level detection (for Type-A and Type-B: *ibid.* at § 5.8.2.6.4) or a timeout since last signal transition (for Type-C: *ibid.* at § 5.8.3.6.1).

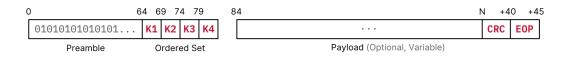

also the line between two different forms of packet. The general format of a packet is shown in figure 2.

Common to each format are the preamble—an alternating sequence of 1s and 0s to be used to synchronise clocks—and the 'ordered set', which identifies the kind of packet and hence whether it includes a payload. The ordered set is a resilient data structure composed of four 5-bit codes known as 'K-codes', and its valid values are defined in such a way that they can be identified when three of four K-codes are present and correct.<sup>14</sup> Table 1 lists relevant ordered sets.<sup>15</sup>

Table 1. USB-PD physical layer ordered sets.

| Set                   | K-code | S      |        |        | Purpose                        |

|-----------------------|--------|--------|--------|--------|--------------------------------|

| Control transmissions |        |        |        |        |                                |

| Hard_Reset            | RST-1  | RST-1  | RST-1  | RST-2  | Hard-resets devices and cable. |

| Cable_Reset           | RST-1  | Sync-1 | RST-1  | Sync-3 | Hard-resets cable.             |

| Data transmissions    |        |        |        |        |                                |

| SOP                   | Sync-1 | Sync-1 | Sync-1 | Sync-2 | Messages for ports.            |

| SOP'                  | Sync-1 | Sync-1 | Sync-3 | Sync-3 | Messages for source eMarker.   |

| SOP"                  | Sync-1 | Sync-3 | Sync-1 | Sync-3 | Messages for sink eMarker.     |

A control transmission is terminated by its ordered set.<sup>16</sup> Data transmissions, on the other hand, include a variable-length payload, a check code, and a terminator after their ordered set.<sup>17</sup> The payload is simply the message forwarded by the protocol layer, while the 'CRC' (cyclic redundancy check) field is a check code calculated from the payload and used to verify that it has not been damaged or corrupted in transit.<sup>18</sup> The 'EOP' field is a K-code used to indicate that the end of

- <sup>14</sup> See USB-PD revision 3.0 [9] at § 5.4.

- <sup>15</sup> Two further ordered sets, SOP'\_Debug and SOP"\_Debug, are defined but have no specified purpose or meaning: see USB-PD revision 3.0 [9] at § 5.6.1.2.4 and 5.6.1.2.5.

- <sup>16</sup> Note that this separation is not expressly reflected in the USB-PD specification [9], and so each control transmission is independently specified in this format: *ibid.* at § 5.6.4 and 5.6.5.

- <sup>17</sup> See USB-PD revision 3.0 [9] at Figure 5-3.

- <sup>18</sup> See USB-PD revision 3.0 [9] at § 5.6.1.4, 5.6.2, and 5.6.3.

the data has been reached. An in-band terminator like 'EOP' would normally impact the ability of a channel to carry arbitrary data by preventing the use of whichever value represents the terminator. However, the design of USB-PD's media conversion service makes this a non-issue.

The conversion to the USB-PD data channel line format involves two steps: the mapping of payload data to a '4b5b' line-coded form,<sup>19</sup> and then final conversion to the electrical signals transmitted between devices. That line code—which uses 5-bit symbols to represent 4 bits of data—is intended to ensure that there are sufficient transitions between  $\theta$  and 1 to allow a receiver to remain synchronised with the transmitter, but its use has the added benefit of enabling use of in-band signalling that does not interfere with data transmission; a 5-bit code can represent 32 symbols, but only 16 symbols are needed to represent all 4-bit values. USB-PD uses the remaining symbols to represent its K-codes, including the packet terminator sent with data transmissions.

Once line coding has been applied, the resultant symbols are converted to electrical signals in one of two ways. For USB Type-C cables, the biphase mark coding scheme (see 2.2.3) is used and the output is transmitted over the 'CC' wire in the cable.<sup>20</sup> Where instead a Type-A or Type-B cable is attached, a binary frequency-shift keying scheme (see 2.2.4) is used and is transmitted over the USB power conductor  $V_{BUS}$ .<sup>21</sup> Formally, the latter scheme is deprecated in USB-PD revision 3.0. Its use is permitted by revision 2.0 with the caveat that, where used by a source with a USB Type-C receptacle, the BMC scheme must be supported and must be used for initial attempts at communication.<sup>22</sup>

Irrespective of the scheme used, data is sent over the line in little-endian order.23

#### 2.2.3 Biphase mark coding (BMC)

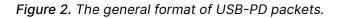

The USB Power Delivery specification sources its definition of biphase mark coding from BS EN 60958-1 [11],<sup>24</sup> a standard for an audio interface implemented in S/PDIF. Onto this definition it adds its own electrical parameters: a signalling voltage swing of 1.125 volts nominal, a data rate of 300 kilobits per second, and a host of timing parameters which dictate how quickly and slowly the signal can swing from one voltage to another.

The scheme itself is relatively simple. A clock operates at twice the data rate, and

- <sup>19</sup> See USB-PD revision 3.0 [9] at § 5.3.

- <sup>20</sup> See USB-PD revision 3.0 [9] at § 5.8 and revision 2.0 [10] at § 5.8.3.

- <sup>21</sup> See USB-PD revision 2.0 [10] at § 5.8.2.

- <sup>22</sup> See USB-PD revision 2.0 [10] at § 5.8.4. That section also imposes other similar requirements, such as that any hard reset must be signalled using both schemes if both are supported.

- <sup>23</sup> See USB-PD revision 3.0 [9] at § 5.5 and revision 2.0 [10] at § 5.5.

- <sup>24</sup> *Op. cit.* at § 4.2 *per* USB-PD revision 3.0 [9] at § 5.8.

each bit is encoded in a 'unit interval' of two clock pulses. The line starts at zero and its state inverts at the beginning of each unit interval. A measurement of the line is taken on each clock pulse and the value represented in a unit interval is determined by comparing the two measurements that occur during the interval: equal represents 0, and inequal represents 1. An example is shown in figure 3.

Figure 3. Biphase mark coding (BMC) of example binary data.

The result of this is that line state does not, in isolation, map to data. This is especially clear in comparing UI-0 and UI-3—each represents 0, but the line is high in UI-0 and low in UI-3. Similarly, when encoding 1, it can be seen in UI-2 and UI-4 that the line state may move through either low-to-high or high-to-low depending on the previous state of the line.

#### 2.2.4 Binary frequency-shift keying (BFSK)

Conceptually, USB-PD revision 2.0's binary frequency-shift keying scheme is even simpler than BMC. A carrier wave (nominally 23.2MHz) is injected onto the USB power conductor  $V_{BUS}$  and its frequency is modulated up or down by 500kHz to transmit either a 1 or  $\theta$ , respectively.<sup>25</sup> Practically, the complexity of the BFSK scheme lies in its use of high-frequency signals and in the requirement for transmitters to use 'continuous phase' BFSK, where no abrupt change in phase is permitted when switching between frequencies.<sup>26</sup>

## 2.3 USB Type-C

Much as USB was intended to be a universal interface for devices with data and power connections, USB Type-C is intended to be a universal connector that can provide a USB data connection, source enough power for most purposes through

- <sup>25</sup> See USB-PD revision 2.0 [10] at § 5.8.2. The wave function is not normatively stated, but a sine wave is what would be conventionally expected and the informative Appendix C (*ibid.* at C.1.2) suggests the use of a sine wave carrier in testing for power converter noise.

- <sup>26</sup> If, for example, two independent oscillators are running at 23.7MHz and 22.7MHz, the two will not be in phase. This can be seen by comparing  $y_1 = \sin(23.7x)$  and  $y_2 = \sin(22.7x)$ . At x = 0.3314,  $y_1$  is at 100% amplitude and  $y_2$  is at 94.57% amplitude. Simply switching between the two oscillators would distort the output wave as the amplitude would instantaneously drop 5.43%. As the signal is no longer a pure sine wave, it introduces undesirable frequency components.

USB-PD, and host other interfaces as required with well-defined extensibility.<sup>27</sup>

The Type-C specification was standardised in BS EN IEC 62680-1-3. This project will work to the 2018 edition [12] of the standard.

Before Type-C's definition, USB connectors were generally asymmetric and indicated the role the device would assume:<sup>28</sup> a USB host always had a Type-A receptacle and a USB device always had a Type-B receptacle. This simplified connection and ensured a connection was always valid. The Type-C connector does neither—it is horizontally symmetric and so can be inserted 'upside-down', and the same connector is used for USB hosts and devices. As a result, a given pin on a receptacle may become connected to either of two wires in a cable, and a user may invalidly attach a host to a host or a device to a device.

To enable this to work, BS EN IEC 62680-1-3 defines a system which provides means of detecting role, orientation, and power-sourcing capability. Using pairs of resistances connected to each of the two CC wires, a source can verify that it is attached to a sink, determine how the cable is oriented, establish whether the cable requires power, and advertise a basic power level to the sink. Although not especially closely related logically, each of the means is dealt with in this section because of their close electrical relationship. Figure 4 illustrates this scheme.<sup>29</sup>

Figure 4. Presence and role resistances (Rp-Rd) on the USB Type-C 'CC' wire.

In this figure, Ra is the impedance presented by the cable electronics, if present.

As discussed in 2.2, each port has independent power and data roles: a source provides power to a sink and is, on attachment, the downstream-facing port (or the host). To enable power role detection, a source independently pulls each CC

<sup>29</sup> This diagram is based on Figure 4-5 in BS EN IEC 62680-1-3 [12].

<sup>&</sup>lt;sup>27</sup> For example, USB Type-C can host DisplayPort (*per* [12] at § 5.1.4), the analogue signals normally transmitted over 3.5mm jacks (*ibid.* at Appendix A), Thunderbolt [50], and HDMI [51].

<sup>&</sup>lt;sup>28</sup> Note that special USB 'On-The-Go' connectors exist and allow exchanging roles, but that the cable type continues to determine role until an exchange is negotiated.

wire up to 5 volts, and a sink independently pulls each wire down.<sup>30</sup> In the cable, one CC wire connects the two cable-ends and the other may be open-circuited or connected to the cable's marker electronics.

These resistances form voltage dividers on each CC wire, and so by measuring the voltage at each midpoint node a source can determine both whether a device is connected and, if it is, how it is oriented. The source uses this to connect its transceiver to the correct CC wire and, if it detects Ra, to attach  $V_{CONN}$  to the wire that will power the cable electronics. The source then energises  $V_{BUS}$  to power the sink and begin USB-PD negotiation.<sup>31</sup>

As noted in 2.2.1, detecting the presence of an electronic marker (as indicated by the presence of Ra) is important in USB-PD negotiation—a source cannot know whether a Type-C cable is capable of carrying more than 3 amps unless it can interrogate the electronic marker to request the cable's rated current.

### 2.4 USB Battery Charging

The first revisions of the USB specification presented USB as a data interface which also provided power. As such, USB hosts were able to supply 2.5 watts in most cases, down to as little as 0.5 watts for low-power ports.<sup>32</sup> This was enough for basic peripherals, but too little to quickly charge the smartphones that were becoming increasingly prevalent in the mid to late 2000s. Manufacturers solved this by introducing their own indication schemes,<sup>33</sup> and it was likely this that prompted the 2007 publication of the USB Battery Charging specification.

The most recent revision of the Battery Charging specification (USB-BC), revision 1.2, was published in 2010 [13]. It is the closest precursor to USB-PD and is the revision this project will refer to.

In contrast with USB-PD, USB-BC is a 'dumb' protocol—no exchange of messages occurs, and all capabilities are instead advertised by adjusting the electrical characteristics of the USB data lines D+ and D-. This is used to allow the device receiving power to distinguish between and adjust its behaviour to accommodate

- <sup>31</sup> See BS EN IEC 62680-1-3 [12] at § 4.5.1.2.1.

- <sup>32</sup> See USB revision 1.1 [52] at § 7.2.1, which defines a unit load as 100mA and states that low-power devices can draw one unit load and high-power devices five unit loads. Further, although seldom implemented, *ibid.* at § 7.1.7.4 and 7.2.3 requires a host to suspend a device which is idle for more than 3ms. Suspension limits current draw to 0.5mA or 2.5mA (2.5 to 12.5mW).

- <sup>33</sup> Examples of such schemes can be found in datasheets for 'Dedicated Charging Port Controllers', such as that for the TPS2513A [63] at § 8.3.

Note that BS EN IEC 62680-1-3 [12] permits other implementations. A source may use a current source instead of a resistor or might pull CC up to a voltage other than 5 volts, while a sink might use a voltage clamp (such as a Zener diode or TL431) rather than a pull-down: see *ibid.* at § 4.11.1 and 4.11.3 with Tables 4-20, 4-21, and 4-28 to 4-32.

five kinds of port:

- Standard Downstream Ports (SDPs), which provide the default USB power level and expect a device to limit the current it draws accordingly;<sup>34</sup>

- Charging Downstream Ports (CDPs), which are largely equivalent to SDPs but permit a device to draw increased current without negotiation;<sup>35</sup>

- Dedicated Charging Ports (DCPs), which have no USB data connection and looser limits on permitted V<sub>BUS</sub> voltage;<sup>36</sup>

- Accessory Charging Adapters (ACAs), which are used to connect the device being powered to a CDP or DCP and another device, enabling it both to receive power and act as a USB host for the other device;<sup>37</sup>

- ACA-Docks, which are conceptually similar to ACAs but use an external non-USB power source and must meet the power requirements of CDPs.<sup>38</sup>

Once attached, the device being powered drives the D+ and D- lines and observes the response: SDPs and DCPs do not respond, but resistances connect the data lines together and the mode of connection changes the voltage measurable on the D- line;<sup>39</sup> a CDP drives D- until it detects the device driving D+, prompting the device to drive D- and measure the voltage on D+;<sup>40</sup> and ACA-Docks both bias the data lines and connect a specified resistance to a dedicated 'ID' contact, each of which the device detects and which are sufficient to unambiguously identify the port as an ACA-Dock.<sup>41</sup> ACA detection relies solely on the resistance on the

- <sup>34</sup> See USB-BC [13] at § 1.4.13. The pull-down resistances mentioned in that section are the standard resistances specified in USB revision 2.0 [53] at § 7.1.1.3 and 7.1.5.1 with Table 7-7.

- <sup>35</sup> A CDP must be capable of sourcing at least 1.5 amps, and a device being powered can draw this before a USB connection is established: see USB-BC [13] at § 4.2.1 with Table 5-2.

- <sup>36</sup> DCPs must be able to source at least 500mA, after which their V<sub>BUS</sub> may droop. If more than 1.5 amps is sourced, or if V<sub>BUS</sub> droops below 2 volts, they may shut down: see USB-BC [13] at § 4.4.1.

- <sup>37</sup> See USB-BC [13] at § 6.1.

- <sup>38</sup> See USB-BC [13] at § 4.3. An ACA takes its sourcing behaviour from its attached charging port, which may be a CDP or DCP. As an ACA-Dock does not use a USB charging port, the standard sets out that the CDP requirements are those that apply.

- <sup>39</sup> An SDP pulls both lines low while a DCP shorts the two lines together: see USB-BC [13] at § 3.2.4.1 and 3.2.4.3. This means that an SDP will present a near-ground voltage on D- while a DCP will present a voltage at almost the same level as was driven.

- <sup>40</sup> As the voltage the CDP uses to drive D- is the same as that a DCP would present, a device proceeds to 'secondary detection' where it establishes if a device is a CDP or a DCP. The CDP does not short the data lines in the way a DCP does, and so D+ measures near ground without the device driving it: see USB-BC [13] at § 3.2.4.2 and 3.2.5.2 with Table 5-1.

- <sup>41</sup> See USB-BC [13] at § 3.2.4.4.

'ID' pin,<sup>42</sup> while Micro ACA detection<sup>43</sup> relies on the 'ID' pin and measuring voltages on the data lines connected to the accessory.<sup>44</sup>

Most relevant to the project is the Dedicated Charging Port behaviour—a USB-PD source which can supply 100 watts will be more than capable of supplying the currents necessary to comply with USB-BC, and in a plug socket form factor such a source is unlikely to require a USB data connection.

<sup>42</sup> See USB-BC [13] at § 3.2.6.

<sup>44</sup> See USB-BC [13] at § 3.2.4.5.

<sup>&</sup>lt;sup>43</sup> A Micro ACA is an ACA with a USB On-The-Go port for the device being powered as well as a USB micro-AB receptacle for the accessory. As On-The-Go enables role swapping, detection is necessary to avoid a violation of the USB specification resulting from two hosts attempting to assert themselves: see USB-BC [13] at § 6.2 and, in particular, 6.2.5.

# 3. Requirements Specification

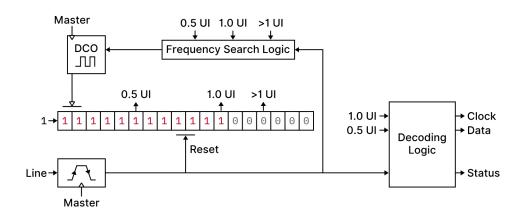

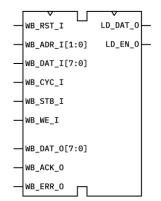

This chapter sets out design and functional requirements for the project. Each is derived from the objectives in chapter 1 and based on the foundations set out in chapter 2. For the purposes of this specification, the structure of the system that the project aims to implement is that shown in figure 5.

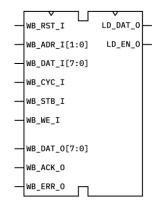

Figure 5. Block diagram of the project system.

In a full USB-PD plug socket system, the system controller would also control or interface with an isolated power converter. This is outwith the project's scope.

## 3.1 Power supply requirements

The PHY must short USB data lines D+ and D– together through a resistance of no more than  $200\Omega$  (3.1.1).

Rationale: This is required by USB-BC [13] at § 4.4.3 and indicates to a USB device that the source is capable of supplying between 500mA and 5 amps without the need for negotiation, subject to voltage droop limits. This will enable fast charging even when a non-USB-PD device is attached.

The PHY must limit  $V_{BUS}$  capacitance to  $10\mu F$  (**3.1.2**) and secure that the impedance between  $V_{BUS}$  and GND exceeds 72.4k $\Omega$  (**3.1.3**) until it detects the attachment of a sink. The PHY must return  $V_{BUS}$  to this state when the sink is detached (**3.1.4**).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.4.2. See also the relevant requirement 3.5.2, which relates to Rp–Rd signalling.

If operating in either of the Disabled or Error Recovery states, the PHY must not drive  $V_{BUS}$  or  $V_{CONN}$  (3.1.5).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.5.2.2.1 and 4.5.2.2.2. See also the related requirement 3.5.3.

The PHY must energise  $V_{BUS}$  to 5±0.25 volts within 275ms of attachment (3.1.6) and de-energise  $V_{BUS}$  to 0.0–0.8 volts within 650ms of detachment (3.1.7).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.11.2 and 4.5.2.2.1 with voltage levels given in USB-PD revision 3.0 [9] in Table 7-21. That Table also restates the requirements as to timing from BS EN IEC 62680-1-3. See also requirements 3.1.5 and 3.2.4, which restrict this requirement.

The PHY must be capable of connecting  $V_{CONN}$  to either CC wire (3.1.8).

Rationale: This is necessary to power Type-C powered cables, which use one of the CC wires to communicate and one as a power source. As Type-C is reversible, it cannot be known prior to attachment which CC wire will be which. Refer to BS EN IEC 62680-1-3 [12] at § 4.5.1.2.1 and 4.5.1.3.1.

The PHY must energise  $V_{CONN}$  to 3.0–5.5 volts no more than 2ms after energising  $V_{BUS}$  (3.1.9), must be capable of sourcing at least 1 watt on  $V_{CONN}$  (3.1.10), and must disconnect  $V_{CONN}$  within 35ms of detachment (3.1.11).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.4.3, 4.5.2.2.9, and 4.11.2 with the parameters given in Tables 4-5 and 4-25. Note that  $V_{\text{CONN}}$  may be energised before  $V_{\text{BUS}}$ .

The PHY must connect a discharge resistance Rdch of  $30-6120\Omega$  between  $V_{CONN}$  and ground if the sink is detached when  $V_{CONN}$  is energised and until  $V_{CONN}$  is at a voltage of 0.8 volts or less (3.1.12).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.4.3 and 4.5.2.2.6 with Tables 4-5 and 4-6 and Figure 4-12. See also requirement 3.2.4, which relates to PHY behaviour during  $V_{CONN}$  discharging.

#### 3.2 Physical layer behavioural requirements

The PHY must not consider an attachment to be made unless, after 100–200ms of first detecting the attachment, the states of the CC wires are unchanged (**3.2.1**).

Rationale: This required by BS EN IEC 62680-1-3 [12] at § 4.5.2.2.8.2 with parameters taken from Table 4-27. The waiting period is intended to allow values to settle after initial attachment. See also requirement 3.5.2, which relates to the detection of attachment and orientation.

The PHY must monitor for detachment (**3.2.2**) and must consider detachment to have occurred if the CC wire initially connected to Rd is open-circuited (**3.2.3**).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.5.2.2.9.2.

Whilst discharging  $V_{CONN}$  in fulfilment of requirement 3.1.12, the PHY must not heed attachments until  $V_{CONN}$  has discharged below 0.8 volts (3.2.4).

Rationale: This is a requirement of BS EN IEC 62680-1-3 [12] at § 4.5.2.2.6 with the voltage level given in Table 4-6.

The PHY must not begin USB-PD configuration before  $V_{BUS}$  has reached the voltage specified in requirement 3.1.6 (3.2.5).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.5.2.2.9.1.

The PHY must not attempt to communicate with a cable's electronic marker unless at least 50ms has elapsed since  $V_{CONN}$  was energised (3.2.6).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.9.1.

#### 3.3 BMC transceiver requirements

The BMC transceiver must be capable of operating in separate modes for USB-PD revision 2.0 and USB-PD revision 3.0 (**3.3.1**).

Rationale: This is necessary to support relatively minor differences in BMC transmission between the two revisions.

The BMC transceiver must be capable of connecting to either CC wire (3.3.2).

Rationale: This is necessary to accommodate the reversibility of Type-C. Refer to BS EN IEC 62680-1-3 [12] at § 4.5.1.2.1 and 4.5.1.3.1.

The BMC receiver must present an input impedance of at least  $1M\Omega$  (3.3.3). Rationale: This is a requirement of USB-PD revision 3.0 [9] at § 5.8.6.

The BMC receiver must be capable of synchronising its clock with that of a transmitter using the preamble prepended to each transmission (**3.3.4**) and must tolerate a clock frequency in the range 540–660kHz (**3.3.5**).

Rationale: BMC relies on taking line measurements in time with a clock but does not provide a clock line between devices, and so the preamble must be used instead to derive a clock. The USB-PD specification also permits data rates in the range 270–330kbps, and so the clock frequencies given above must be supported.

The BMC receiver must recognise a line voltage of 1.05-1.20 volts as a logic high and a line voltage of 0.6 volts or less as a logic low (**3.3.6**). If the line is idle, the BMC receiver must ignore noise with an amplitude of 0.3 volts or less (**3.3.7**).

Rationale: USB-PD revision 3.0 [9] at § 5.8.1 and 5.8.4 specifies 1.05–1.20 volts as the swing to be produced by the transmitter's driver. A logic low voltage is not given, but it is reasonable to assume a target of 0 volts and reasonable to take 0.6 volts (half the maximum logic high voltage) as an upper bound. This is supported by BS EN IEC 62680-1-3 [12] in Figure 4-36. The noise level requirement is derived from *ibid.* at § 5.8.2.2.

The BMC receiver must measure and decode transmissions on the line using the biphase mark coding scheme defined in USB-PD revision 3.0 [9] (**3.3.8**).

Rationale: This is a requirement of the USB-PD specification, *ibid.* at § 5.8.

The BMC receiver must be capable of receiving a signal which complies with the limits and masks in USB-PD revision 3.0 [9] at § 5.8.2.2 (**3.3.9**).

Rationale: This is necessary to support the rise and fall times a transmitter is permitted to exhibit.

The BMC transmitter must be capable of signalling at 600kHz (3.3.10).

Rationale: This is necessary to give the 300kbps nominal data rate specified in USB-PD revision 3.0 [9] at § 5.8.4.1.

The BMC transmitter must begin a transmission by driving the line low (**3.3.11**). Rationale: This is a requirement of USB-PD revision 3.0 [9] at § 5.8.1.

The BMC transmitter must not begin a transmission unless a period of at least 25µs has elapsed since the line became idle, since the transmitter concluded its previous transmission, or since the previous frame was received (**3.3.12**).

Rationale: This is required by USB-PD revision 3.0 [9] at § 5.7, 5.8.5.4, and 5.8.6.1, and parameters are given in Tables 5-18 and 5-19. The 'line idle' condition occurs when there are fewer than three transitions on the line within the last 12 to 20µs. Note that the 25µs includes the periods in requirements 3.3.16 to 3.3.20. See also requirement 3.3.13 for collision-avoidance signalling timing. This requirement is mirrored for BFSK by requirement 3.4.19.

In USB-PD revision 3.0 mode, the BMC transmitter must signal 'transmit no go' at least 16 to 20ms before beginning a transmission (**3.3.13**) and must otherwise signal 'transmit ok' (**3.3.14**).

Rationale: This is required by USB-PD revision 3.0 [9] at § 5.7 and is used to avoid collisions on the line. These states are signalled using the CC wire pull-up Rp, which indicates that a device is a source and advertises its current capability. It can be seen from Table 5-13 (*ibid.*) with BS EN IEC 62680-1-3 [12] at Table 4-20 that 'no go' is signalled by Rp =  $22k\Omega \pm 5\%$  and 'ok' by Rp =  $10k\Omega \pm 5\%$ . The initial value of Rp to be used is specified in requirement 3.5.1. Note that no equivalent provision is made for USB-PD revision 2.0. See also requirement 3.3.12 for timing around when a transmission may begin.

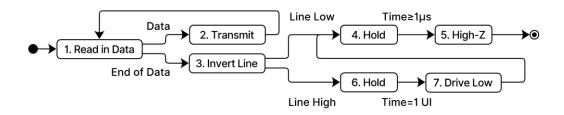

After completing a transmission, the BMC transmitter must invert the state of the line (3.3.15). If this causes the transmitter to drive the line low, the transmitter must hold the line low for at least  $1\mu$ s (3.3.16) and present a high impedance within  $23\mu$ s (3.3.17). If this causes the transmitter to drive the line high, the transmitter must hold the line high for one unit interval (3.3.18), drive the line low for at least  $1\mu$ s (3.3.19), and present a high impedance within  $23\mu$ s (3.3.20).

Rationale: This is a requirement of USB-PD revision 3.0 [9] at § 5.8.1, illustrated in Figures 5-11 through 5-14. The final transition is intended to ensure the final bit is correctly received. For the avoidance of doubt, the period in 3.3.17 includes the period in 3.3.16. The same is true of 3.3.20 with 3.3.18 and 3.3.19.

The BMC transmitter must transmit logic high using a line voltage of 1.125 volts and logic low using a line voltage of 0 volts (**3.3.21**). When not transmitting, the transmitter must present a high impedance to the line (**3.3.22**).

Rationale: The logic high voltage is the nominal voltage swing to be produced by the transmitter's driver *per* USB-PD revision 3.0 [9] at § 5.8.1 and 5.8.4. The logic low level is not specified but, given the phrasing 'swing' used for logic high, it is reasonable to assume a swing from reference potential is intended. Presenting a high impedance is implicit in the requirement to use a tristate driver. Also see requirements 3.3.16 to 3.3.20 relating to timing on transmission completion.

The rise and fall times of the BMC transmitter output must comply with the limits and masks in USB-PD revision 3.0 [9] at § 5.8.2.1 (3.3.23).

Rationale: This is necessary, *per op. cit.*, to limit coupling to other conductors in the USB cable. The nature of this requirement is such that it makes the most sense to reference the diagrams rather than describe the requirement.

The BMC transmitter must present a capacitance of 200 to 600pF to the line when not transmitting (**3.3.24**).

Rationale: This is a requirement of USB-PD revision 3.0 [9] at § 5.8.5.1.

The BMC transmitter must present an output impedance of 33 to  $75\Omega$  at a frequency of 750kHz (**3.3.25**).

Rationale: This is a requirement of USB-PD revision 3.0 [9] at § 5.8.5.2.

The BMC transmitter must be capable of withstanding without damage a short to ground lasting 120µs (**3.3.26**).

Rationale: This is required by USB-PD revision 3.0 [9] at § 5.8.5.5. This is intended to support the 'fast role swap' functionality of hubs, which is not relevant here.

#### 3.4 BFSK transceiver requirements

The BFSK transceiver must be isolated from the  $V_{BUS}$  bulk capacitance and the power supply by an impedance of at least 80 $\Omega$  at frequencies 20.4–26MHz (3.4.1).

Rationale: This is required by USB-PD revision 2.0 [10] at § 5.8.2.2 with the parameters given in Table 5-17. *Ibid.* at C.1 suggests the use of a 1 $\mu$ H inductance, which provides a 128–163 $\Omega$  impedance, and discusses potential issues in the implementation of the isolation impedance.

The BFSK transceiver must be AC-coupled to  $V_{BUS}$ , or must be rated to withstand the maximum voltage which may become present on that conductor (3.4.2). Rationale: This is required by USB-PD revision 2.0 [10] at § 5.8.2.3. The BFSK receiver must present an input impedance of at least  $15k\Omega \pm 15\%$  at any frequency in the range 19–27MHz (3.4.3).

Rationale: This is a requirement of USB-PD revision 2.0 [10] at § 5.8.2.6.1. Note that the input impedance between  $V_{BUS}$  and ground is determined by the transmitter termination resistance (see requirement 3.4.10).

The BFSK receiver must be capable of synchronising its clock with that of a transmitter using either the carrier transmitted prior to transmission (refer to requirement 3.4.12) or the preamble prepended to each transmission (**3.4.4**) and must be able to synchronise to frequencies in the range 21.8–24.6MHz (**3.4.5**).

Rationale: BFSK uses differing frequencies to encode logic high and logic low. As no marker event occurs in each symbol period (compare with BMC), to decode a sequence of one state (*e.g.*  $11_2$  or  $00_2$ ) it is necessary to rely on timing. A data rate of 300kbps produces symbol periods of 3.33µs, and so a logic-low frequency which persists for 6.66µs can be interpreted as  $00_2$ .

The BFSK receiver must support a carrier frequency of 22.4–24MHz (3.4.6) and must interpret a frequency 450–600kHz slower as a logic low (3.4.7) and a frequency 450–600kHz faster as a logic high (3.4.8), provided that the amplitude of each signal is 55-300 mV<sub>RMS</sub> (3.4.9).

Rationale: These frequencies are set out in USB-PD revision 2.0 [10] at § 5.8.2 and in Table 5-16. The signal amplitude is given in *ibid.* in Table 5-20.

The BFSK transmitter must have a termination resistance of  $62\pm10\Omega$  (3.4.10). Rationale: This is required by USB-PD revision 2.0 [10] at § 5.8.2.5.1.

The BFSK transmitter must comply with the frequency deviation and transmit spectral masks given in USB-PD revision 2.0 [10] at § 5.8.2.5.2 and shown in Figures 5-11 and 5-12 (**3.4.11**).

Rationale: This is necessary to comply with standard limits on emitted noise.

The BFSK transmitter must transmit a carrier-frequency signal for  $1\mu$ s before transmitting a frame (3.4.12) and must not transmit the carrier for more than  $4\mu$ s after the end of the last bit of its transmission (3.4.13).

Rationale: This is a requirement of USB-PD revision 2.0 [10] at § 5.8.2.5.2 with the parameters in Tables 5-14 and 5-18. See also requirements 3.4.14 to 3.4.17.

The BFSK transmitter must use a carrier frequency of 22.4–24MHz (3.4.14), must transmit logic low with a frequency 450–600kHz slower than the carrier (3.4.15), must transmit a logic high with a frequency 450–600kHz faster (3.4.16), and must transmit with a signal amplitude of 100-200mV<sub>RMS</sub> (3.4.17).

Rationale: This is required by USB-PD revision 2.0 [10] at § 5.8.2.4.1 and 5.8.2.5.1 with the parameters in Tables 5-16 and 5-18.

The BFSK transmitter must be capable of signalling at 300kbps (3.4.18).

Rationale: This is required by USB-PD revision 2.0 [10] at § 5.8.1.1.

The BFSK transmitter must not begin a transmission unless a period of at least 25µs has elapsed since the line became idle, since the transmitter concluded its previous transmission, or since the previous frame was received (**3.4.19**).

Rationale: This is a requirement of USB-PD revision 2.0 [10] at § 5.7, 5.8.1.4, and 5.8.2.6.4. Relevant parameters are given in Tables 5-14, 5-17, and 5-20. The 'line idle' condition occurs when no signal in the frequency range 20.4-26MHz is detected on V<sub>BUS</sub> with amplitude of or above 35-55mV<sub>RMS</sub>. Note that the 25µs includes the periods in requirements 3.4.12 and 3.4.13. This requirement is mirrored for BMC by requirement 3.3.12.

#### 3.5 Type-C signalling requirements

The PHY must pull each USB Type-C CC wire up to 5 volts using independent resistances Rp of  $10k\Omega \pm 5\%$  (3.5.1).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.11.1 to indicate that the device is a source capable of sourcing at least 3 amps at 5 volts. Relevant to this requirement is requirement 3.3.14, which requires varying Rp, and requirement 3.5.4, which restricts when Rp may be presented.

The PHY must be capable of detecting whether a CC wire is open-circuited, attached to a sink pull-down resistance Rd of  $5.1k\Omega \pm 20\%$ , or attached to a cable marker electronics resistance Ra of  $800-1200\Omega$  (**3.5.2**).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.5.1.2.1 with Tables 4-20 to 4-22 and is necessary to detect whether a sink is attached and, if it is, how the attaching cable is oriented. See also section 2.3. *Per ibid.* in Table 4-30, a CC voltage of 0.00–0.75 volts is expected for Ra, 0.85–2.45 volts for Rd, and a voltage of 2.75 volts or above for an open circuit. See also requirement 3.2.1, which relates to the process of confirming attachment.

If operating in either of the Disabled or Error Recovery states, the PHY must present an impedance to ground of at least  $126k\Omega$  on each CC wire (3.5.3).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.5.2.2.1 and 4.5.2.2.2 with the minimum impedance figure given in Table 4-23. See also the related requirement 3.1.5.

Whilst discharging  $V_{CONN}$  in fulfilment of requirement 3.1.12, the PHY must not present a pull-up Rp on  $V_{CONN}$  (3.5.4).

Rationale: This is required by BS EN IEC 62680-1-3 [12] at § 4.5.2.2.6.

# 4. Summary of Findings

This chapter summarises the findings made in chapters 5 to 7, which describe the research done to fulfil the requirements in chapter 3.

In summary:

- The biphase mark code transmitter is most easily and reliably implemented with a slew rate-limiting RC filter, buffered and connected to the line through a transmission gate (section 5.2.2);

- The biphase mark code receiver can be implemented largely in digital logic using a reference counter to measure pulse duration, where counting rate is successively approximated using the USB-PD preamble (section 5.3.1);

- The analogue portion of the biphase mark code receiver can use a reference design from USB-PD, where DC bias tolerance is obtained by taking the difference between two cascaded filters and extracting a square wave using a hysteresis comparator fed with the output (section 5.3.3);

- The binary frequency-shift keying transmitter must maintain continuous phase in its output and so can be viably implemented with four orthogonal-frequency oscillators or a tuneable LC oscillator (section 6.2.1);

- The four-oscillator transmitter would use a high-speed switch to connect the appropriate signalling frequency to the line at the start of each data period, minimising distortion but at relatively high cost (section 6.2.2);

- The tuneable LC oscillator transmitter would use a varactor—a DC-controlled variable capacitance—to vary output frequency, with an analogue control signal produced by filtering pulse-width-modulated output (section 6.2.3);

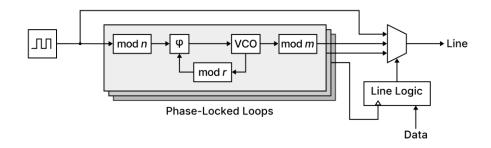

- The binary frequency-shift keying receiver implementation is restricted by loose tolerances (a 0.9–1.2MHz band at any point from 21.8–24.6MHz), and so it could be implemented either by relying on high-speed logic to count pulses or by measuring a phase-locked loop's control signal (section 6.3.1);

- The low signal amplitude permitted by the binary frequency-shift keying scheme would require an automatic gain controller to produce a fixed output suitable for processing (section 6.3.2);

- The digital logic method counts reference clock cycles over a given period and uses changes between counts to detect frequency shifts (section 6.3.3);

- The phase-locked loop-based method divides the linear control signal into eight 350kHz bands and so, with comparators and a priority encoder, can detect frequency shifting by a change in encoder output (section 6.3.4);

- In each case, the output from the binary frequency-shift keying receiver can be decoded by taking the time between frequency shifts and dividing by the number of counts at the carrier frequency, relying on USB-PD's guaranteed maximum durations at any frequency (sections 6.3.3 and 6.3.4);

- A pair of signalling resistances are required for full USB-PD compliance, and transmission gates can be used to control line connection (section 7.1);

- Up to 1 watt of power must be provided to USB Type-C cables and a fastdischarge system must be provided for disconnection, which can be done using a push-pull driver with logic-level MOSFETs (section 7.2).

# 5. Biphase Mark Code Transceiver

This chapter discusses the design and implementation of the biphase mark code (BMC) transceiver required to implement the USB-PD physical layer. Its requirements are set out in section 3.3.

### 5.1 Key concerns

#### 5.1.1 DC bias in received signals

In the general case, communication will be with a device that has no ground other than the ground provided by its USB cable. This cable may stretch several metres, and so may have significant resistance—enough to drop 250mV over its length.<sup>45</sup> This causes ground potential at the sink's end to rise, and so when the sink drives 1.125 volts (logic high) above its ground it may be driving at as much as 1.375 volts above the source's ground. This is noted in Appendix D to USB-PD revision 3.0 [9], which discusses DC bias-immune receiver implementations.